#### **Application Note 1710**

Author: Oscar Mansilla

# intersil

# ISL705xRH and IS706xRH SPICE Model

#### Introduction

The SPICE model for the ISL705XRH and ISL706xRH rad hard supervisory circuits were developed to help system designers evaluate the operation of this IC prior or in conjunction with proto-typing a system design. This model accurately simulates typical performance characteristics at room temperature (+25 °C) such as steady state switching, input voltage and output current transients. Behaviors not supported are temperature analysis, process variation, and AC analysis. Functionality has been tested on ORCAD 10.0 and CADENCE ORCAD 16.3. Other SPICE simulators may be used however the model may require translation.

#### **Reference Documents**

- ISL705ARH, ISL705BRH, ISL705CRH, ISL706ARH, ISL706BRH, ISL706CRH Datasheet, <u>FN7662</u>

- ISL705RH Voltage Supervisory Circuit Evaluation Board User's Guide, <u>AN1650</u>

- ISL706RH Voltage Supervisory Circuit Evaluation Board User's Guide, <u>AN1671</u>

## License Statement

The information in this SPICE model is protected under the United States copyright laws. Intersil Corporation hereby grants users of this macro-model hereto referred to as "Licensee", a nonexclusive, nontransferable license to use this model as long as the Licensee abides by the terms of this agreement. Before using this macro-model, the Licensee should read this license. If the Licensee does not accept these terms, permission to use the model is not granted.

The Licensee may not sell, loan, rent, or license the macromodel, in whole, in part, or in modified form, to anyone outside the Licensee's company. The Licensee may modify the macromodel to suit his/her specific applications, and the Licensee may make copies of this macro-model for use within their company only.

This macro-model is provided "AS IS, WHERE IS, AND WITH NO WARRANTY OF ANY KIND EITHER EXPRESSED OR IMPLIED, INCLUDING BUY NOT LIMITED TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE."

In no event will Intersil be liable for special, collateral, incidental, or consequential damages in connection with or arising out of the use of this macro-model. Intersil reserves the right to make changes to the product and the macro-model without prior notice.

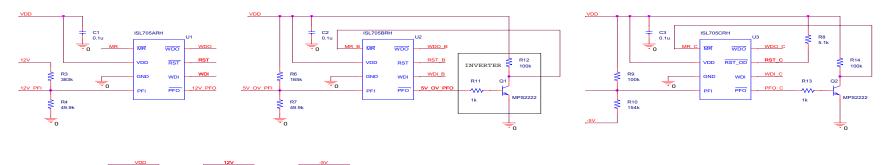

## **Project Files**

The zip file: **ISL705xRH\_ISL706xRH SPICE FILES.zip** contains the project file ISL705ARH.opj to be used in ORCAD simulator. The project file contains two schematics which correlate with the ISL705XRH and ISL706XRH evaluation boards (see Figures 8 and 9). For details on the application schematic refer to the evaluation board user's guide <u>AN1650</u> and <u>AN1671</u>. Each schematic has been set up with a time domain simulation profile for quick evaluation of the model. The schematic pages may be accessed through the main directory window in ORCAD (see Figure 1).

| 🛅 C:\Documents and Settings\omansill\Desktop\ISL70                                                                                                                         | <u>- 🗆 ×</u> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Analog or Mixed A/D                                                                                                                                                        |              |

| 💼 File 🔩 Hierarchy                                                                                                                                                         |              |

| Design Resources Jusi705arh.dsn Jusi705arh.dsn Design Cache Jusi705_APP_CIRCUIT Design Cache |              |

FIGURE 1. APPLICATION SCHEMATIC LOCATION

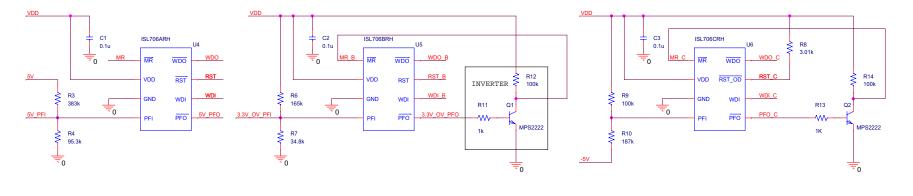

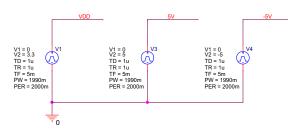

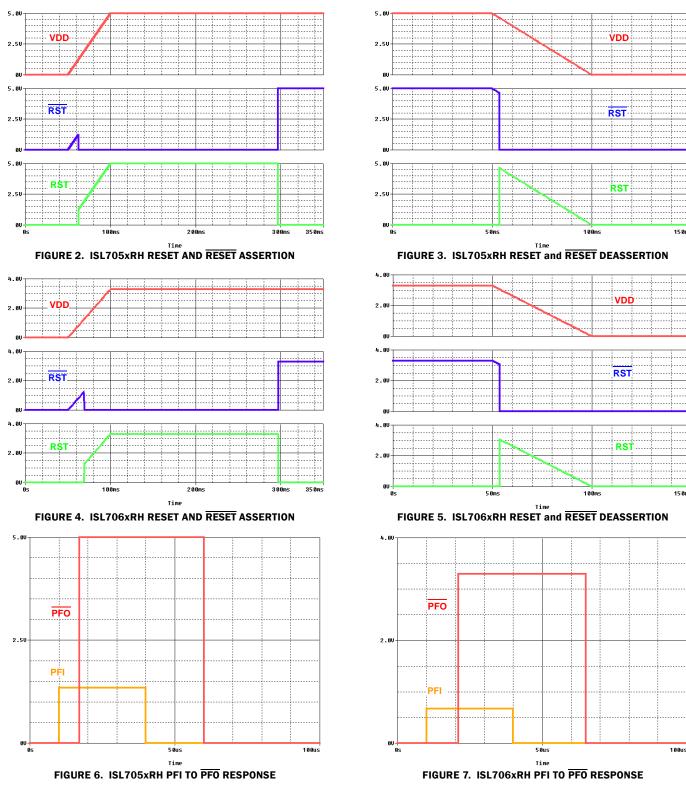

Figures 2 through 7 show simulation results of the RESET and PFI transient response. These can be compared to Figure 8 through 13 of the datasheet for model accuracy.

#### **Model Parameter List**

The model has been developed with a single netlist with multiple variables that are automatically modified to meet IC parameters when the part is placed in an ORCAD schematic from the model library. If the user would like to import the netlist to another SPICE simulator the variables must be entered manually. The parameter list spreadsheet maps the variable state to the corresponding version of the IC, so the user can easily modify the netlist and import the model to other SPICE simulators.

1

#### **Simulation Performance Curves**

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the Application Note or Technical Brief is current before proceeding.

For information regarding Intersil Corporation and its products, see www.intersil.com

100us

150ns

15 Øns

VDD

RST

RSŤ

-----

3 intersil

SECTION 1 (ISL705ARH)

SECTION 2 (ISL705BRH)

SECTION 3 (ISL705CRH)

FIGURE 8. ISL705xRH SIMULATION APPLICATION SCHEMATIC

intersil

4

SECTION 1 (ISL706ARH)

SECTION 3 (ISL706CRH)